# Analysis of a Simple Approach to Modeling Performance for Streaming Data Applications

Jonathan C. Beard Roger D. Chamberlain

Work supported by:

#### **Outline**

- We introduce a simple model to estimate throughput and inform buffering capacity

- The model is tailored to stream processing

- Is applicable to applications deployed on heterogeneous architectures

- We empirically evaluate the proposed model and discuss instances where it works and where it might not

Supercomputing Lab

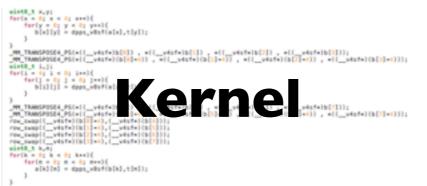

#### Stream Processing Intro - Kernel

```

1 streams [[ Output ]] Work( InputOne, InputTwo )

2 {

3         X = InputOne.get();

4         Y = InputTwo.get();

5         out = do_something( X, Y );

6         Output.push( out );

7 }

```

#### Stream Processing Intro - Kernel

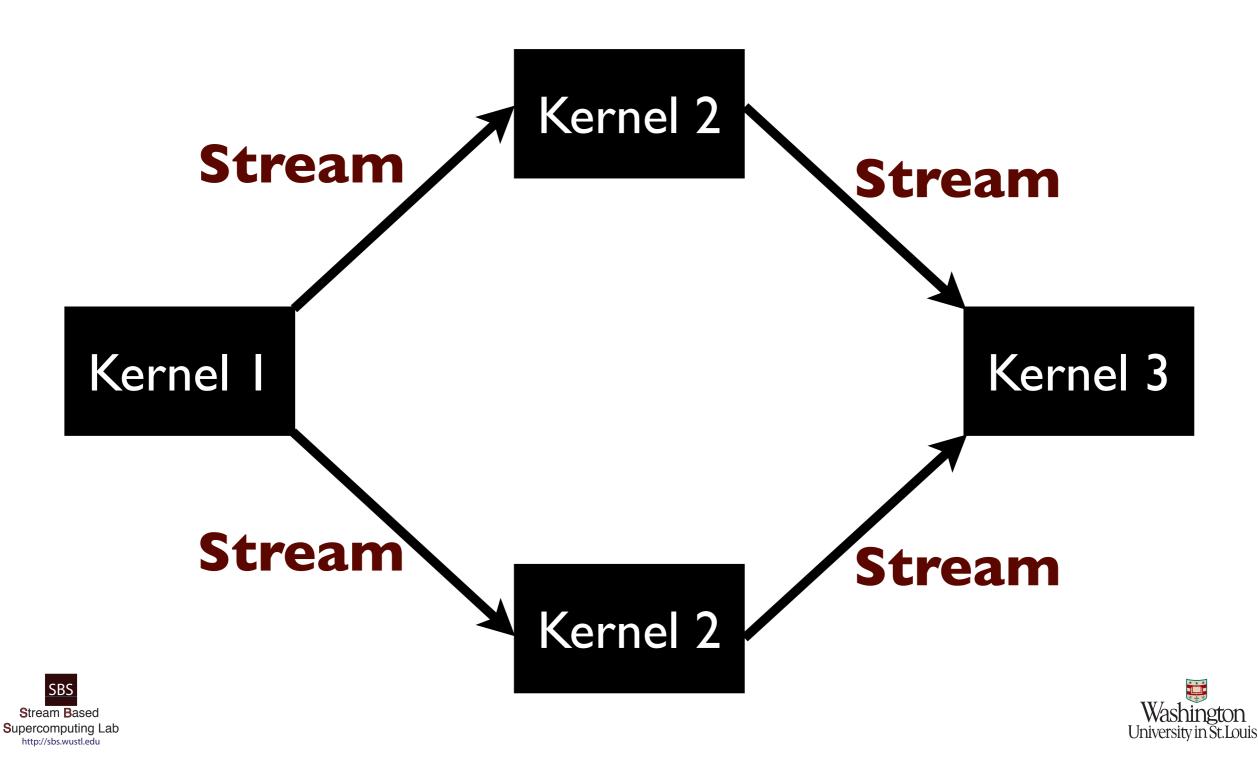

#### Stream Processing Intro - Streams

#### Stream Processing Intro - Languages

- Academic Systems: Auto-Pipe, Brook, Cg,

S-Net, Streamlt, and Streams-C

- Commercial Systems: Impulse C and IBM's System S

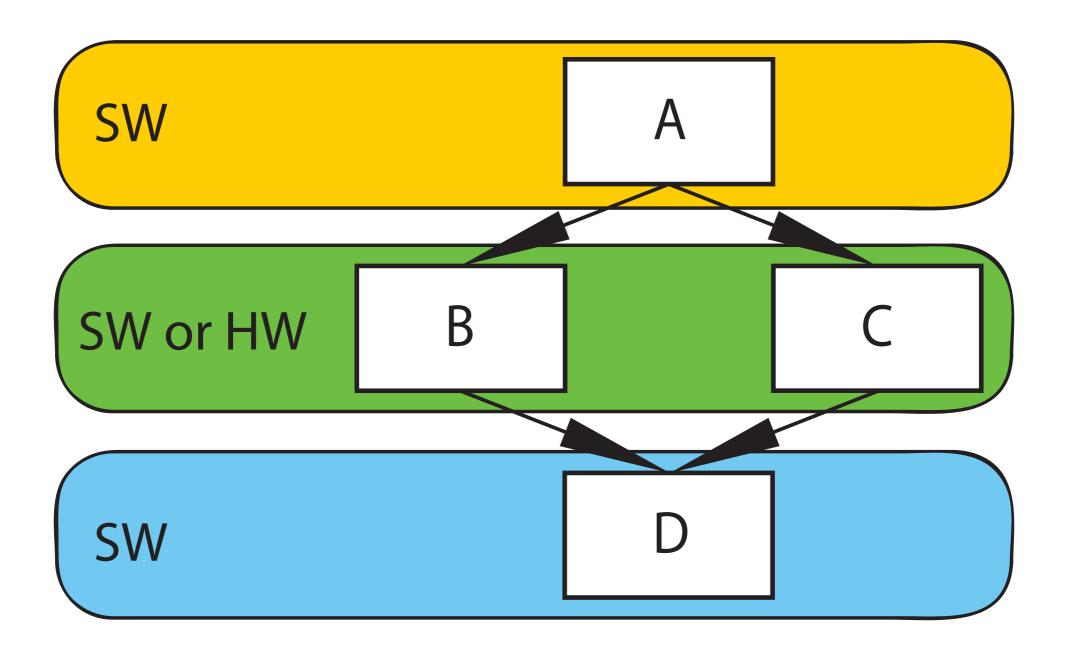

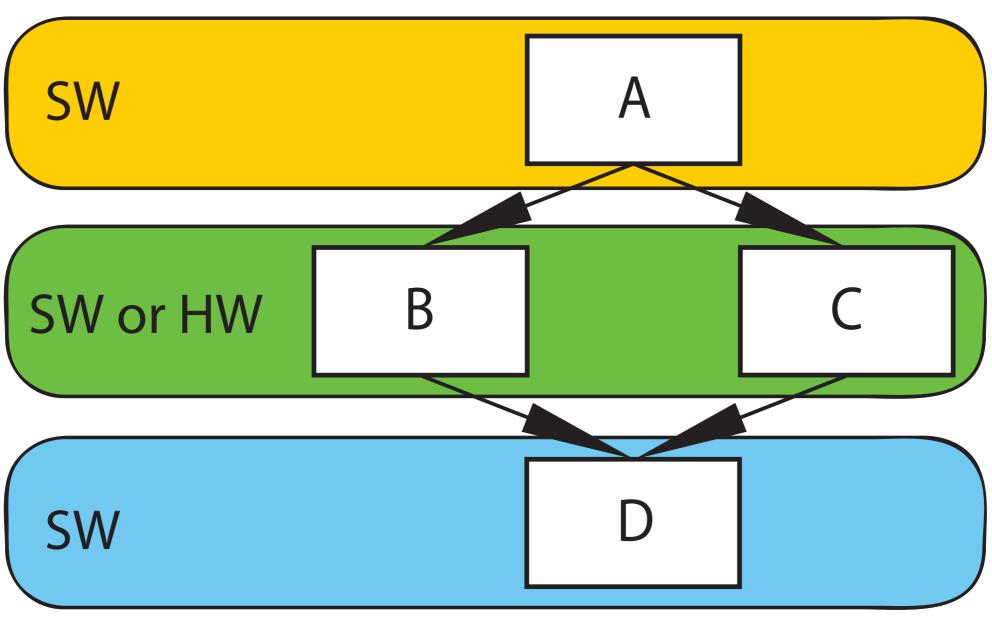

#### Stream Processing Intro - Mapping I

#### Multicore chips

Intel Xeon E7 (10-core)

AMD Opteron 6300 (16-core)

IBM Power7 (8-core)

#### **Specialized Co-Processors**

Intel Phi (61-core)

General Purpose Graphics Processor (GPGPU)

Field

Programmable

Gate Array

(FPGA)

Washington

University in St. Louis

#### How does our kernel perform on each compute resource?

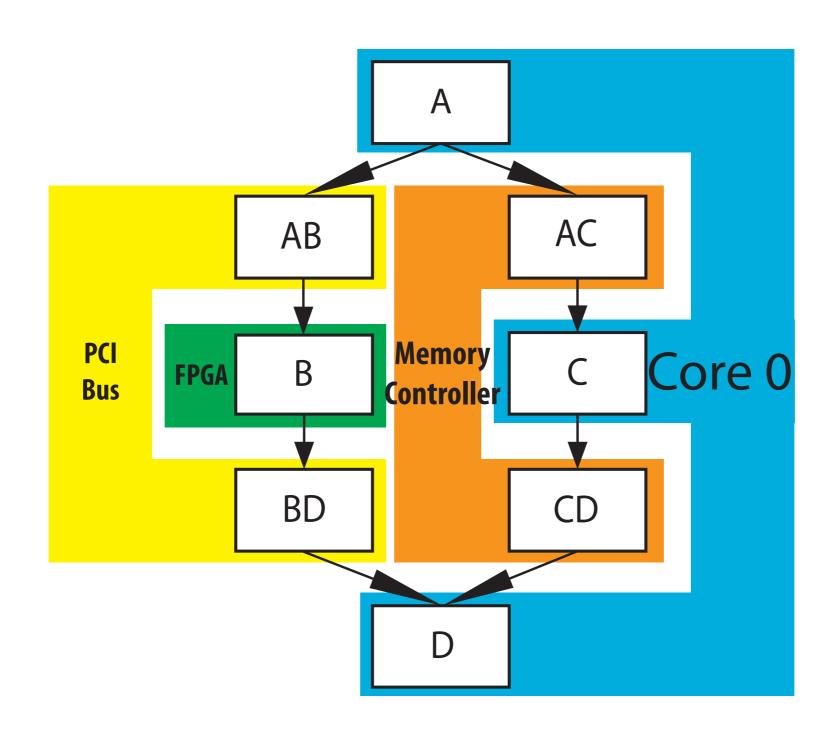

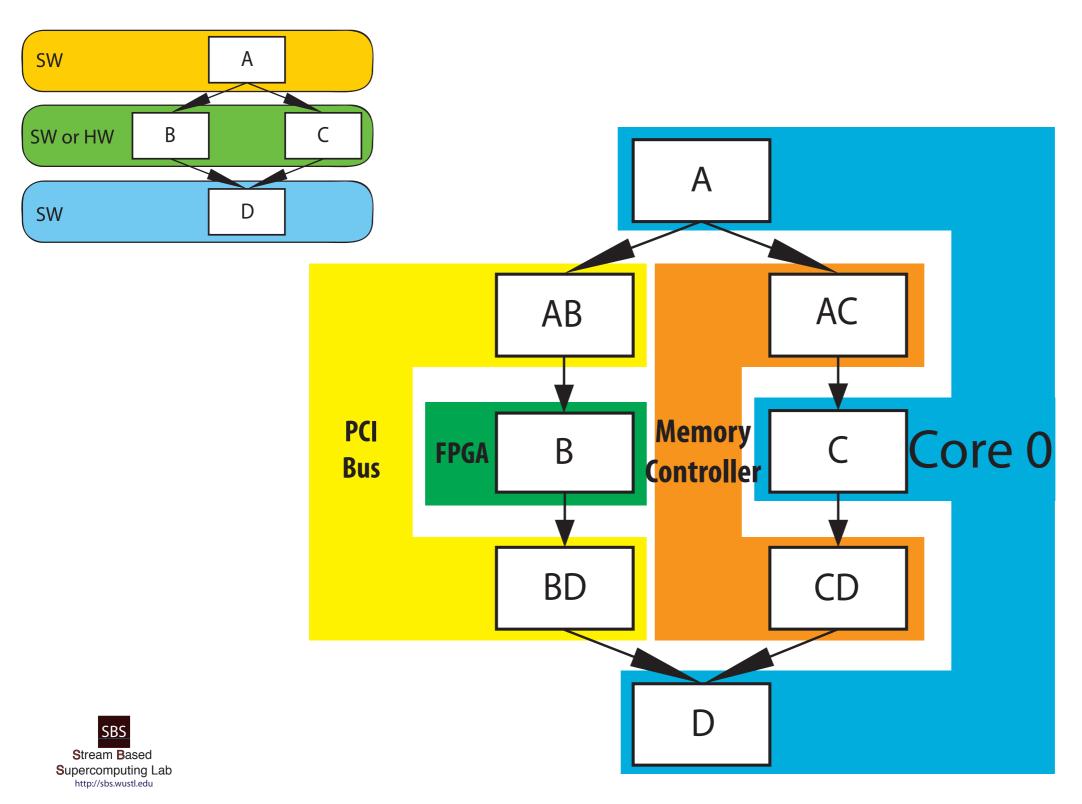

#### Stream Processing Intro - Mapping 3

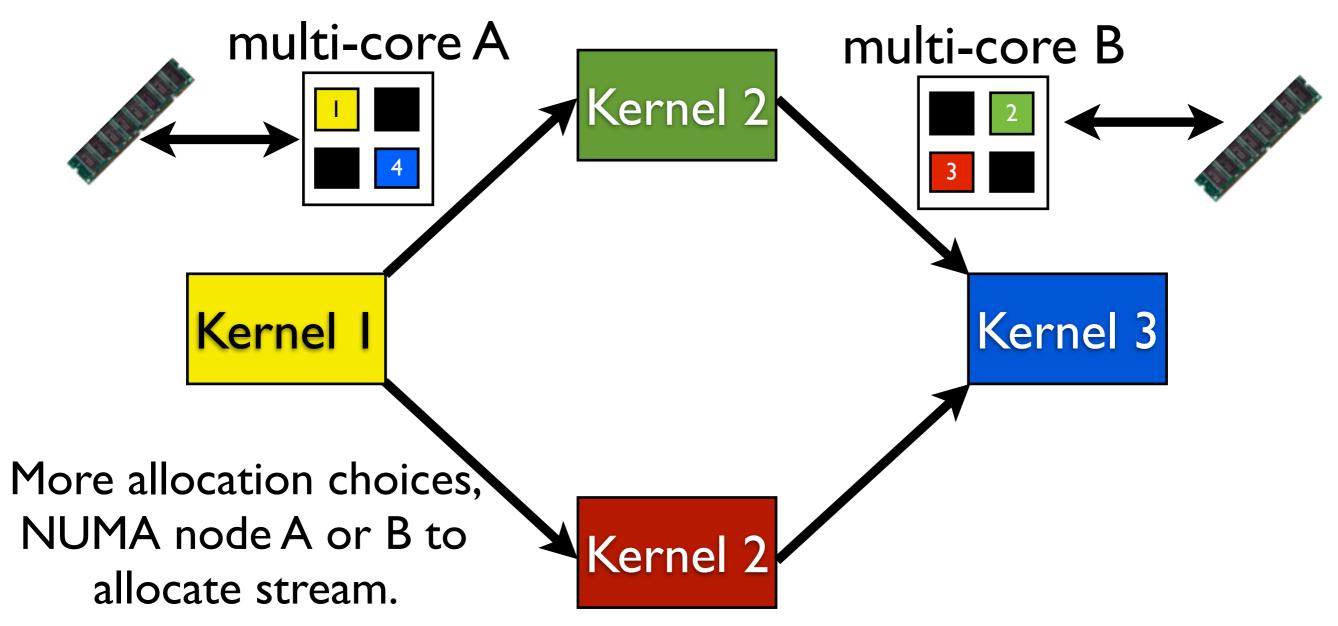

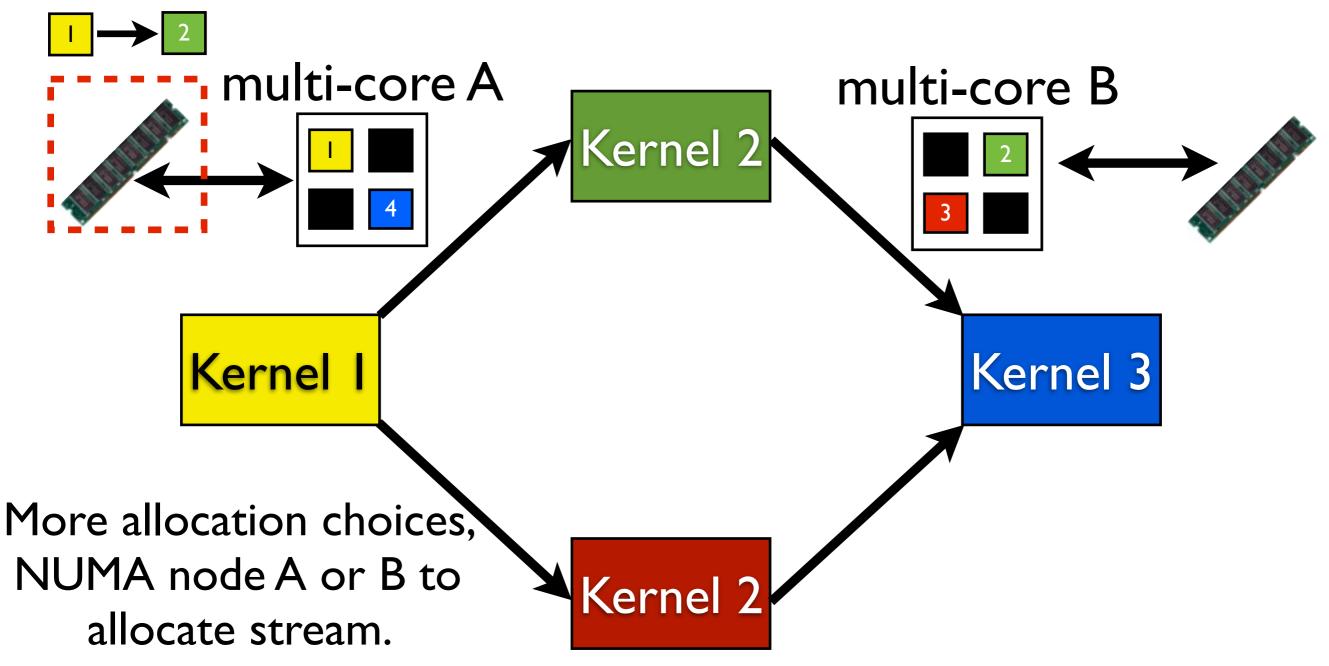

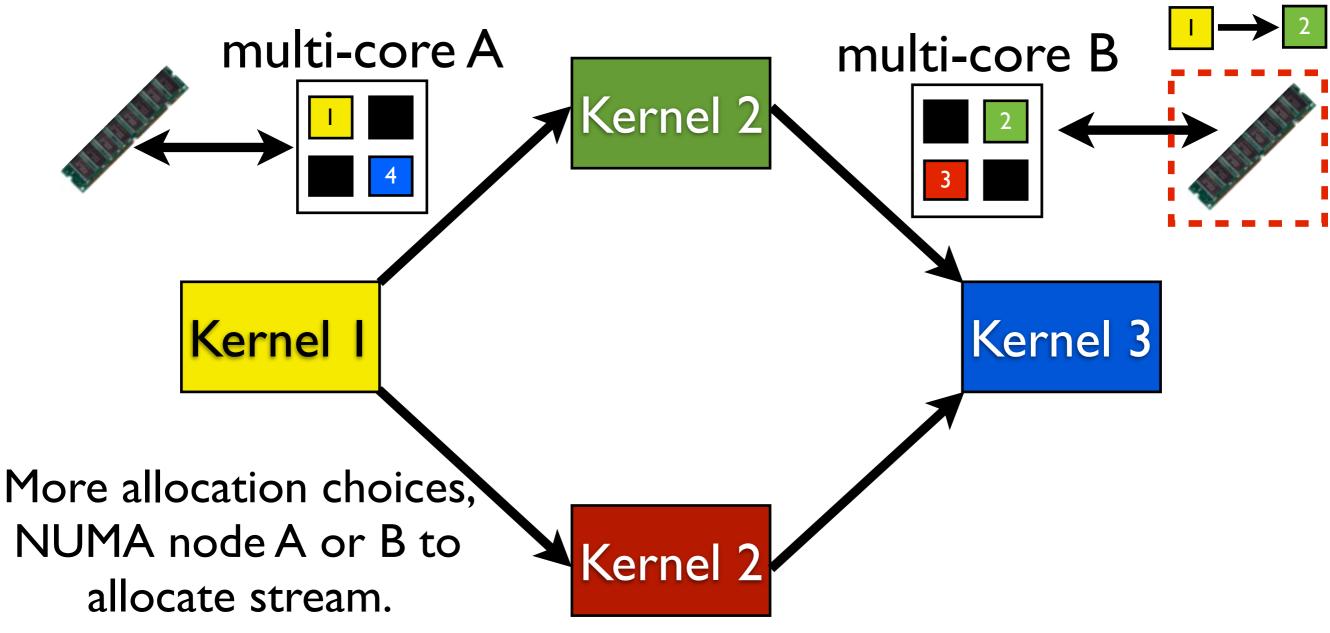

## Stream Processing Intro - Mapping 3

#### Stream Processing Intro - Mapping 3

#### **Application and Implementations**

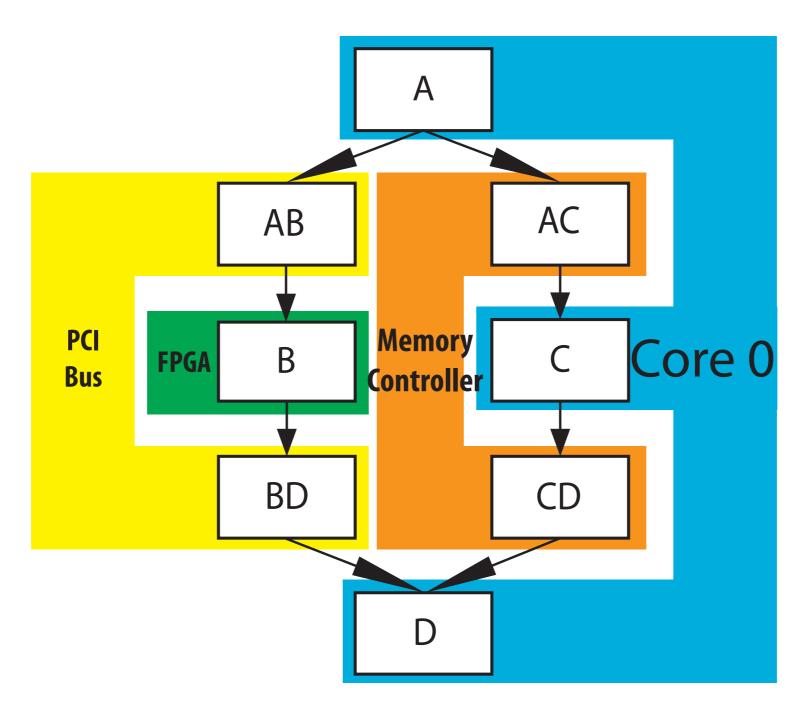

# A Hardware Mapping

#### Hypothesis

Can we calculate achievable throughput and place an upper bound for necessary buffering capacity?

## **Modeling Assumptions**

- The system being modeled is at steady state

- Arrival process is Poisson

- Service times are exponentially distributed.

- Buffers are infinite with non-blocking reads and writes.

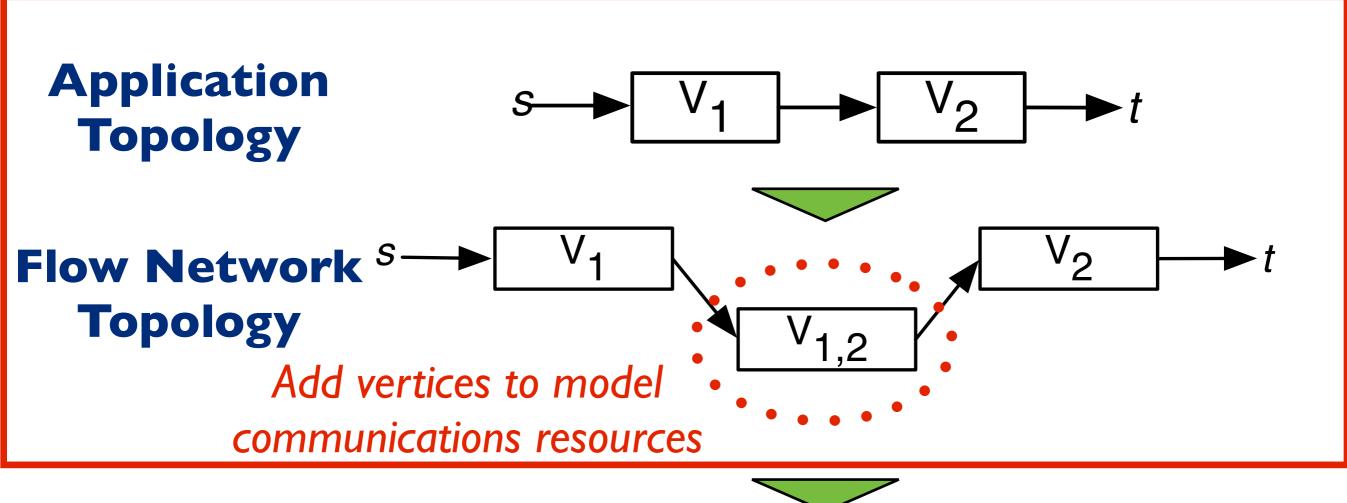

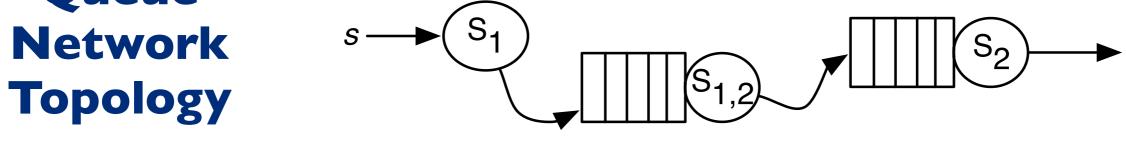

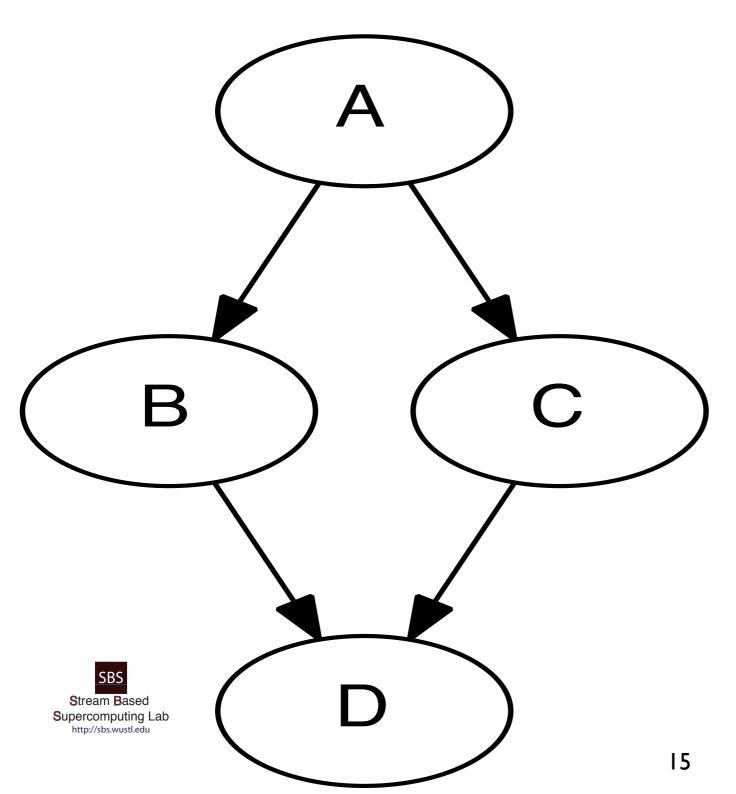

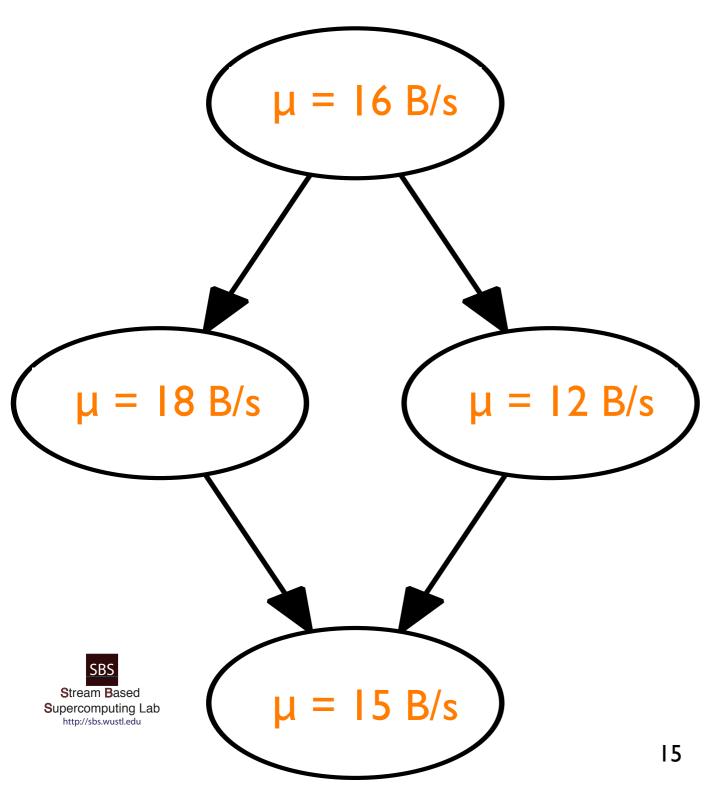

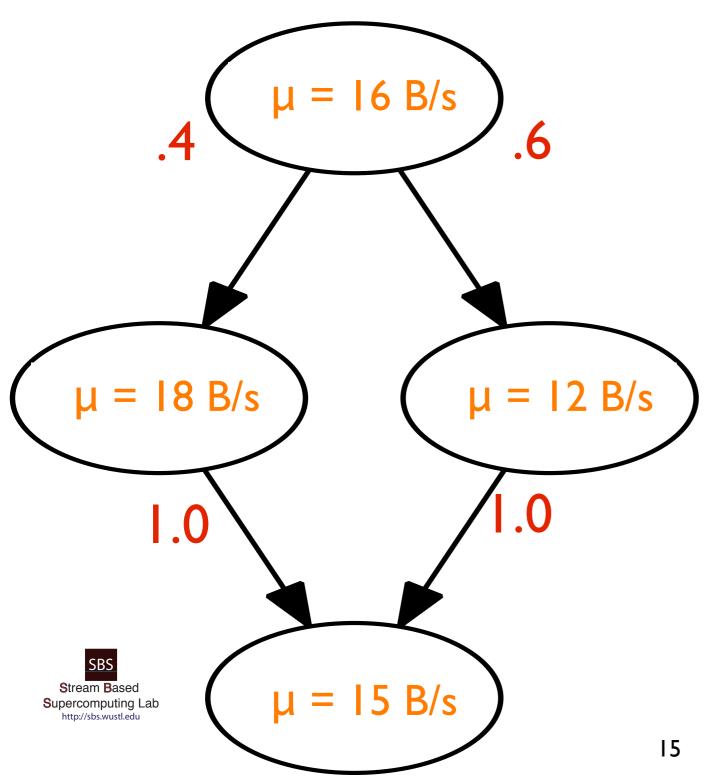

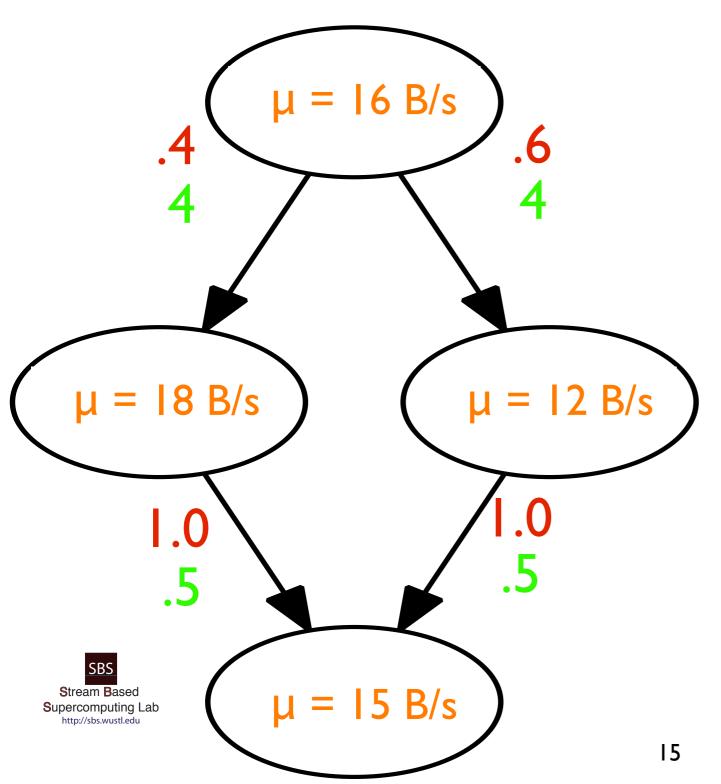

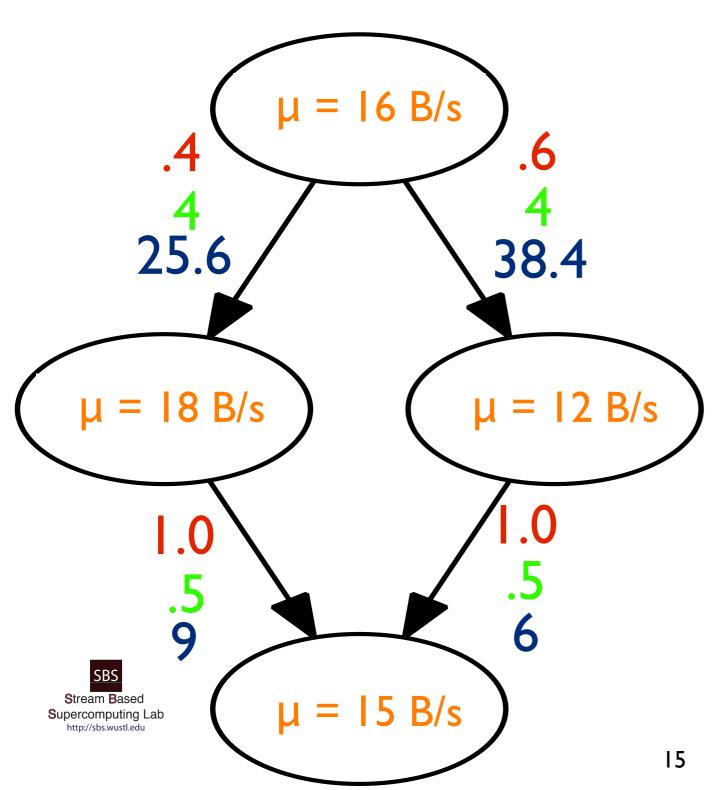

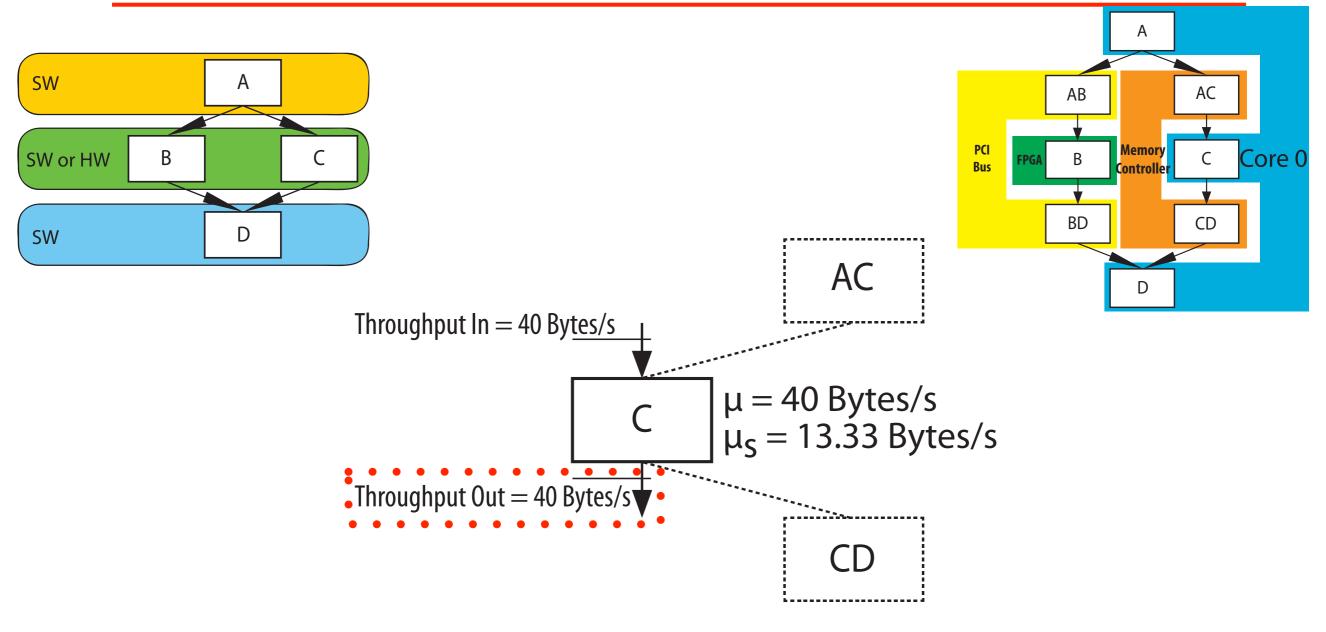

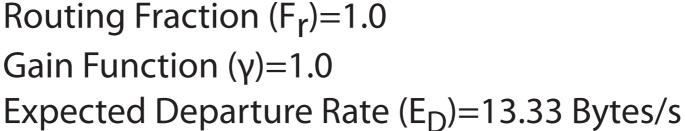

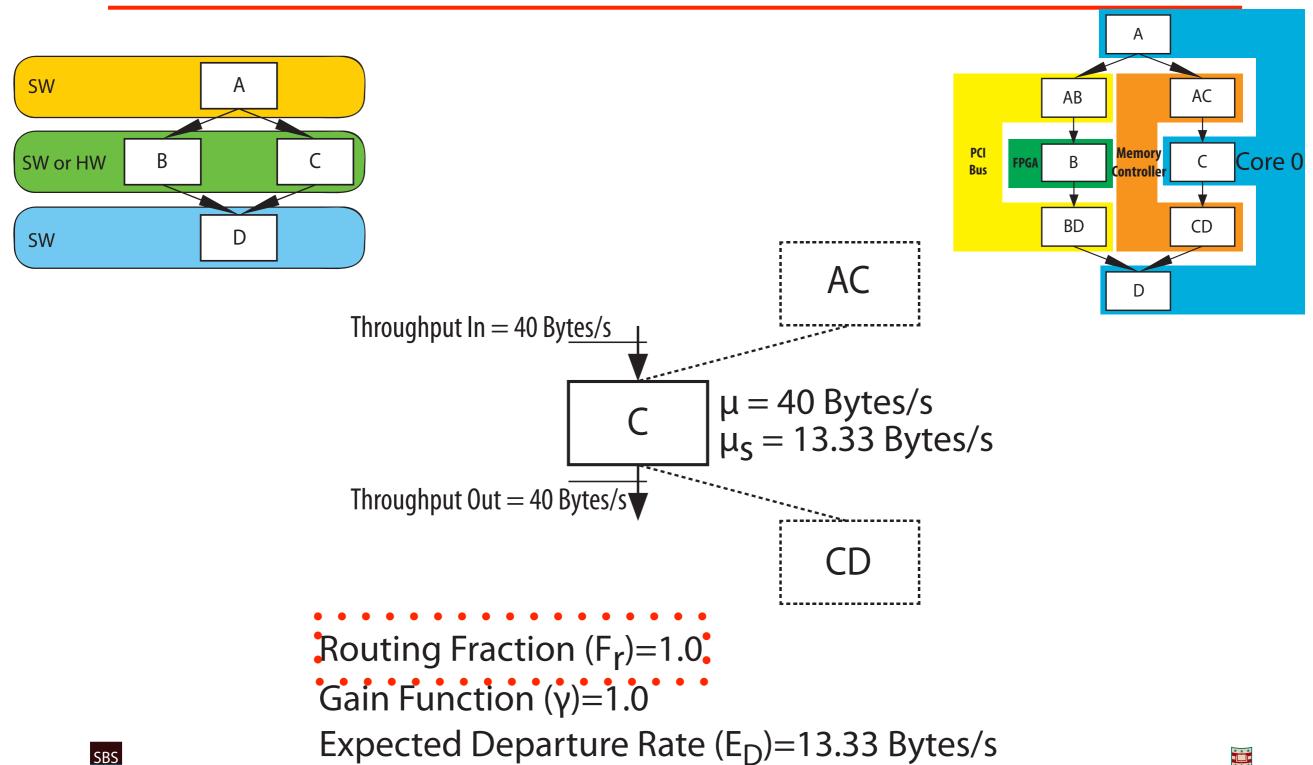

#### Overall Model Layout

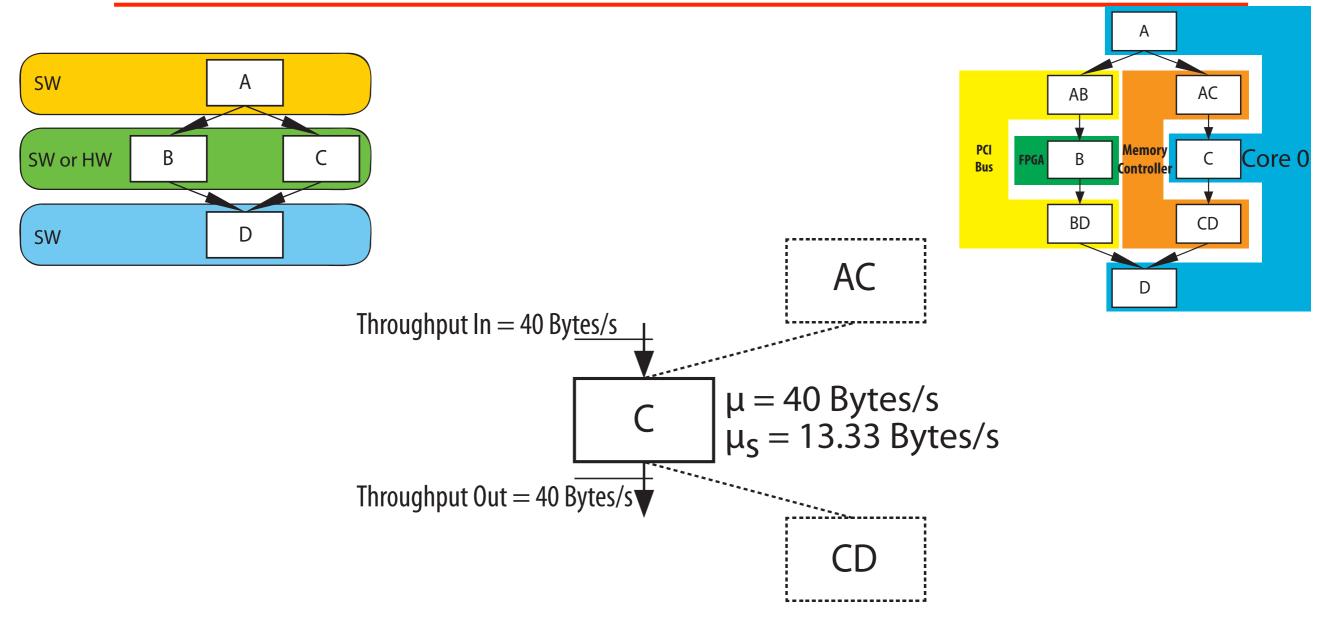

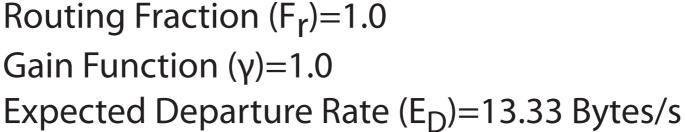

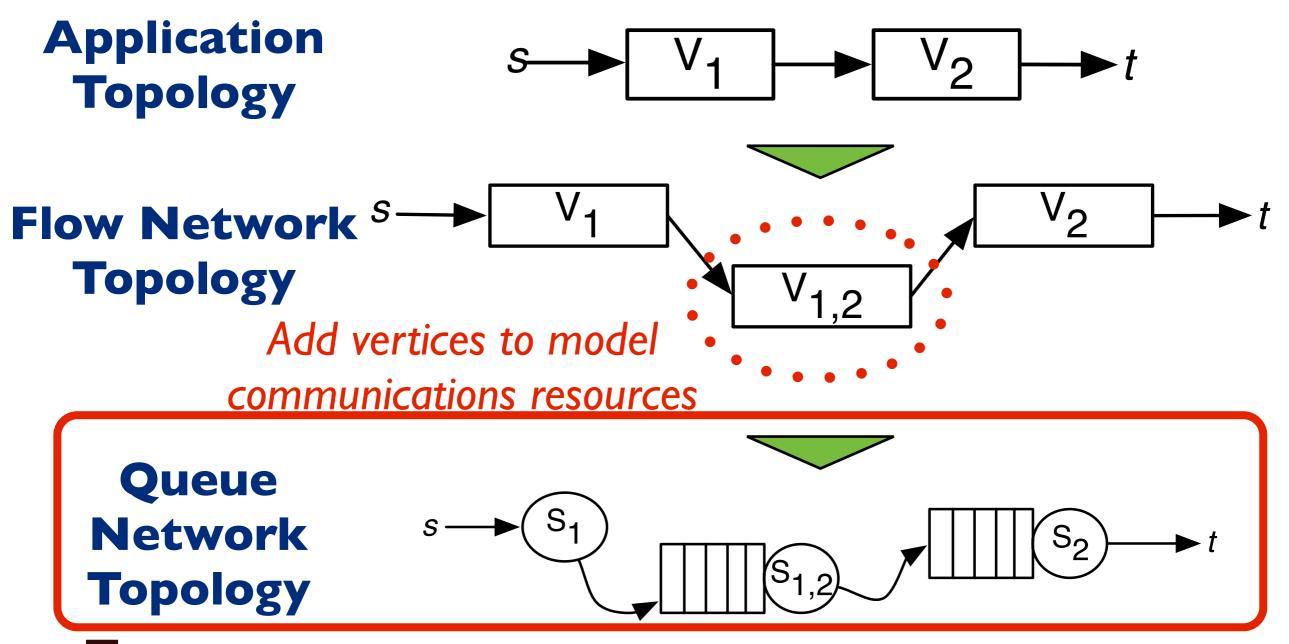

**Application Topology** Flow Network <sup>S</sup> **Topology** Add vertices to model communications resources **Queue** Network **Topology**

## **Overall Model Layout**

# **Q**ueue **Network**

# Flow Model Filtering

# Filtering - Gain or Loss of Data 64-bit Data Packet Kernel 32-bit Data Packet

# Flow Model Filtering

# Filtering - Gain or Loss of Data Kernel 64-bit Data Packet 32-bit Data Packet Routing 60% Kernel Data In 40%

University in St. Louis

Stream Based

Supercomputing Lab

- service rate of kernel

- service rate of kernel

F<sub>r</sub>- fraction of data along kernel out-edges

- service rate of kernel

F<sub>r</sub>- fraction of data along kernel out-edges

y - gain function of

upstream kernel

C - capacity for each edge product of:

- service rate of kernel

F<sub>r</sub>- fraction of data along kernel out-edges

# What about sharing?

# What about sharing?

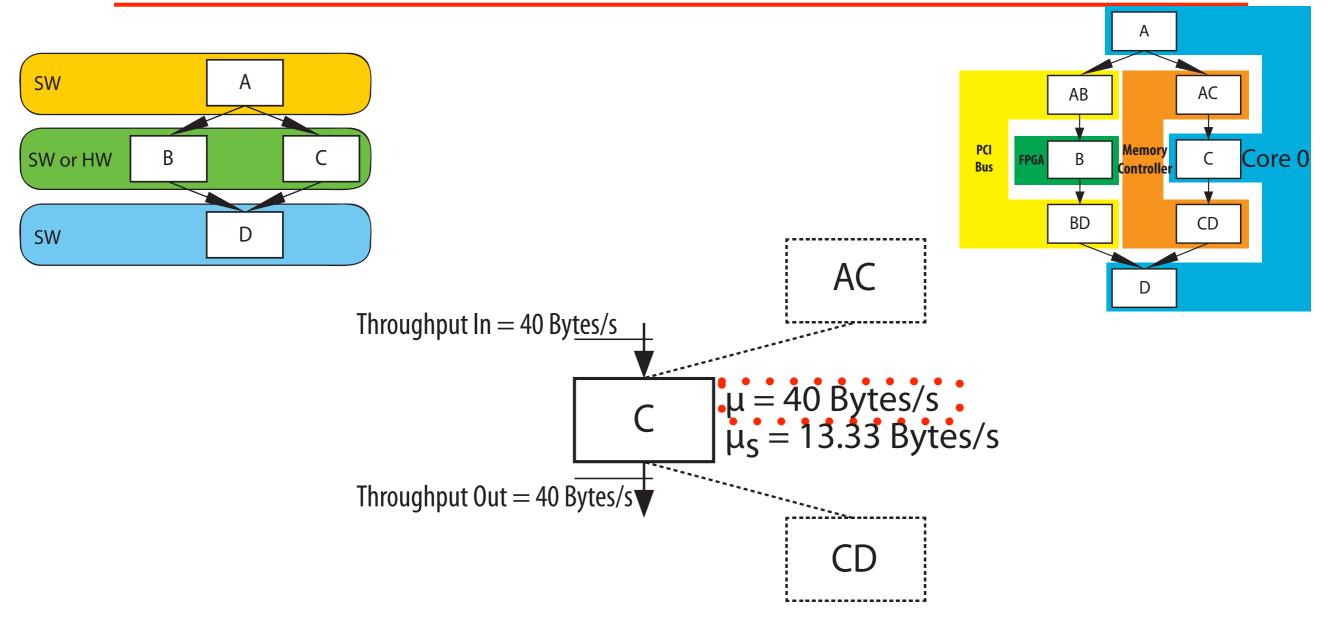

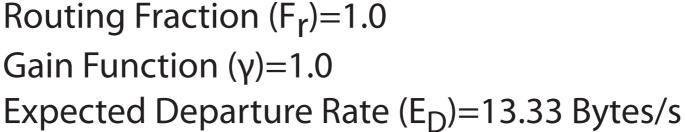

- Multicore(s) Fair Sharing, even division of processing capacity

- FPGA(s) are shared non-temporally via area

- PCI Bus Fair Sharing, even division of bandwidth

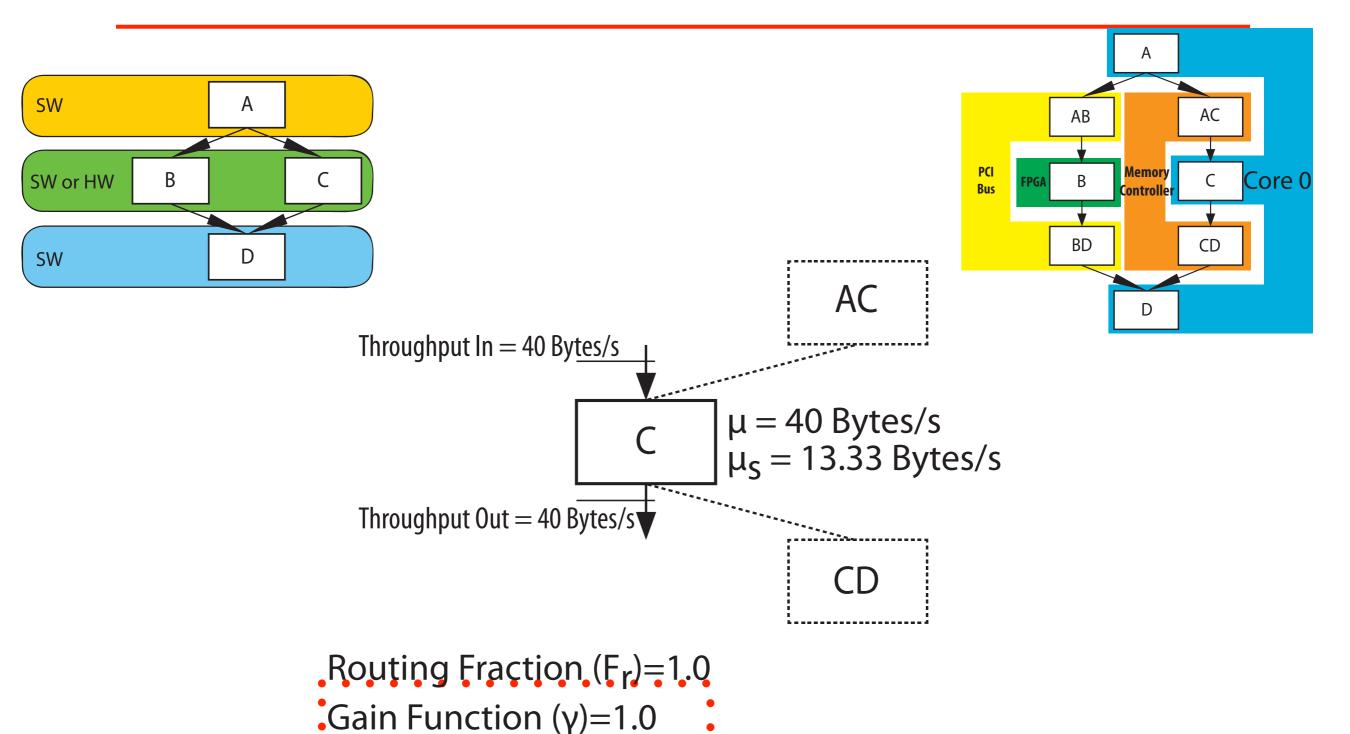

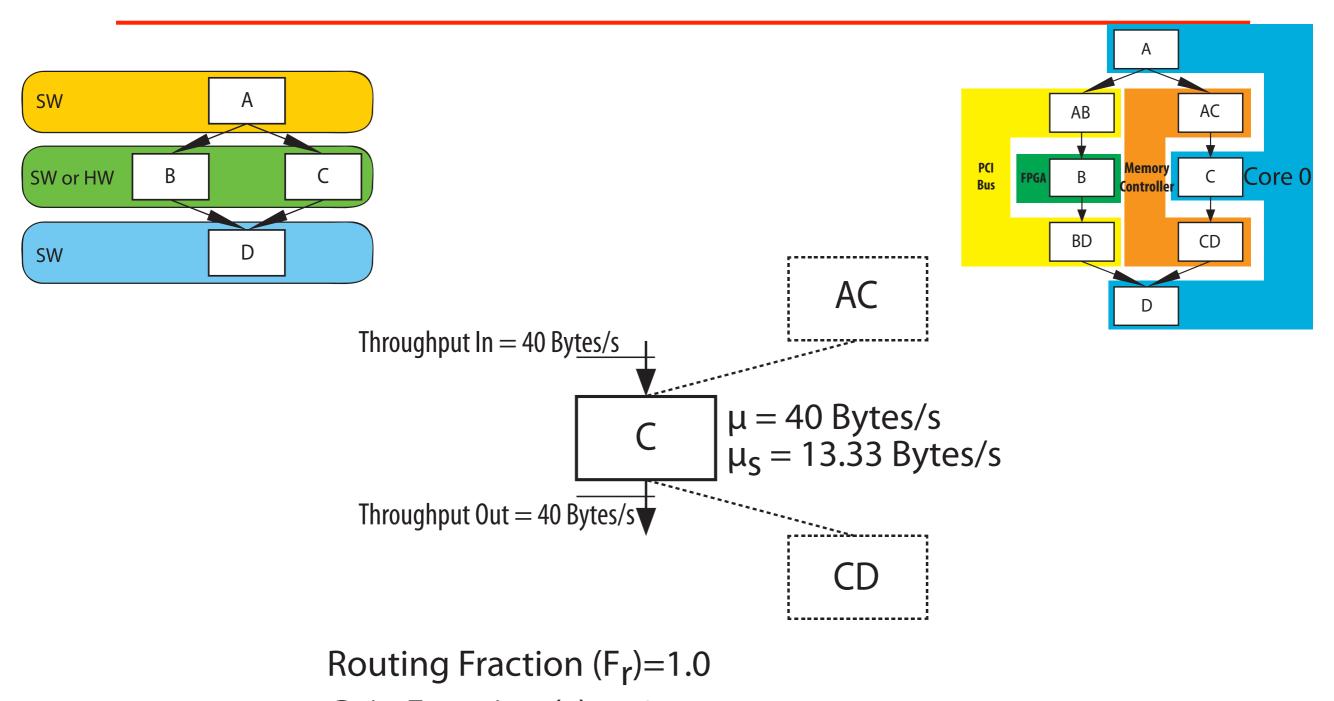

Gain Function  $(\gamma)=1.0$

Expected Departure Rate (E<sub>D</sub>)=13.33 Bytes/s

#### Flow Model

#### Conservation of Flow

$$\sum_{j|(i,j)\in E_F} f(\overrightarrow{V_iV_j}) - \sum_{j|(j,i)\in E_F} f(\overrightarrow{V_jV_i}) = \begin{cases} + & i = s \\ 0 & i = \text{circulation} \\ - & i = t \end{cases}$$

#### **Edge Capacity Constraint**

$$f(\overrightarrow{V_i}\overrightarrow{V_j}) \leq C(\overrightarrow{V_i}\overrightarrow{V_j})$$

#### **Routing Constraint**

$$\frac{f(\overrightarrow{V_i}\overrightarrow{V_j})}{\sum_{x=1}^N f(\overrightarrow{V_i}\overrightarrow{V_x})} = R(\overrightarrow{V_i}\overrightarrow{V_j})$$

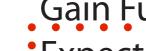

## **Example finished**

#### **Steps Recap:**

- Start with a mapped application topology

- Parameterize the model

- Set the edge capacity equal to the expected departure rate

- Solve for maximum flow

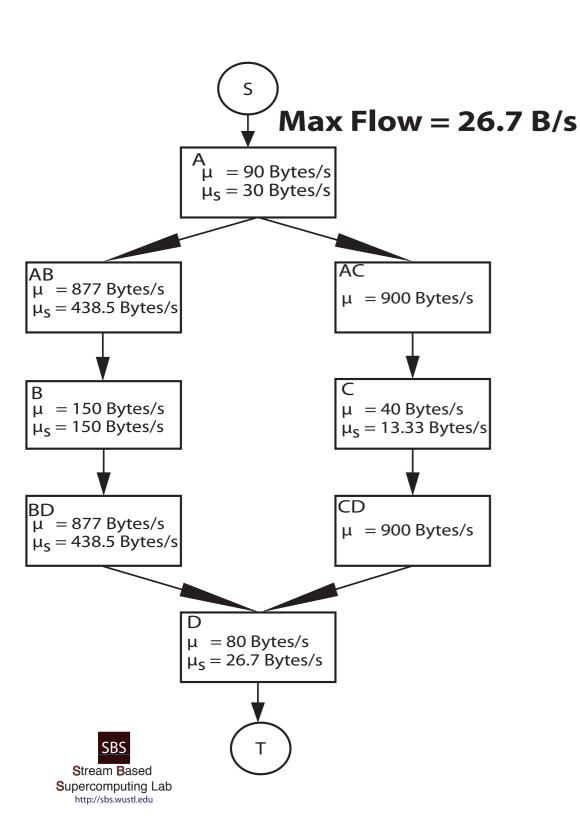

## **Testing Methodology**

- Test the model on multiple real applications (JPEG encode, DES encrypt).

- Generate random synthetic applications to explore a wider range of application topologies.

- Randomly map applications to available hardware using uniform random process.

- Measure throughput and queue occupancy on generated Application / Hardware mappings at each stream (edge).

## **Synthetic Application Stats**

| Statistic                             | Mean                      | Std. Deviation |

|---------------------------------------|---------------------------|----------------|

| Number of Vertices                    | 21                        | 17.52          |

| Kernels per Resource                  | 3.6                       | 3.51           |

| Gain or Loss                          | 0.98                      | 1.03           |

| Routing Probability (F <sub>r</sub> ) | 0.585                     | 0.340          |

| Service Time (µ)                      | Varies, mean 20 µs        |                |

| Packet Size                           | Varies, I 6-Bit to 64-Bit |                |

| Implementations                       | Hardware and Software     |                |

#### **Utilized Hardware**

| Specification | Machine I (x 2)             | Machine 2                    |

|---------------|-----------------------------|------------------------------|

| CPU           | I2 x 2.4 GHz AMD<br>Opteron | 4 x 3.1 GHz Intel<br>Xeon E3 |

| FPGA          | 2 x Virtex-4 LX 100         | None                         |

| RAM           | 32GB DDR2                   | 8GB DDR3                     |

#### Flow Model Results

## **Overall Model Layout**

Stream Based

Supercomputing Lab

# M/M/I Occupancy Model

→ Service Rate  $=\frac{\lambda}{\mu}, P_K = 10^{-7}] = \frac{\log(\frac{P_L}{1-P_L})}{\log(\rho)}$

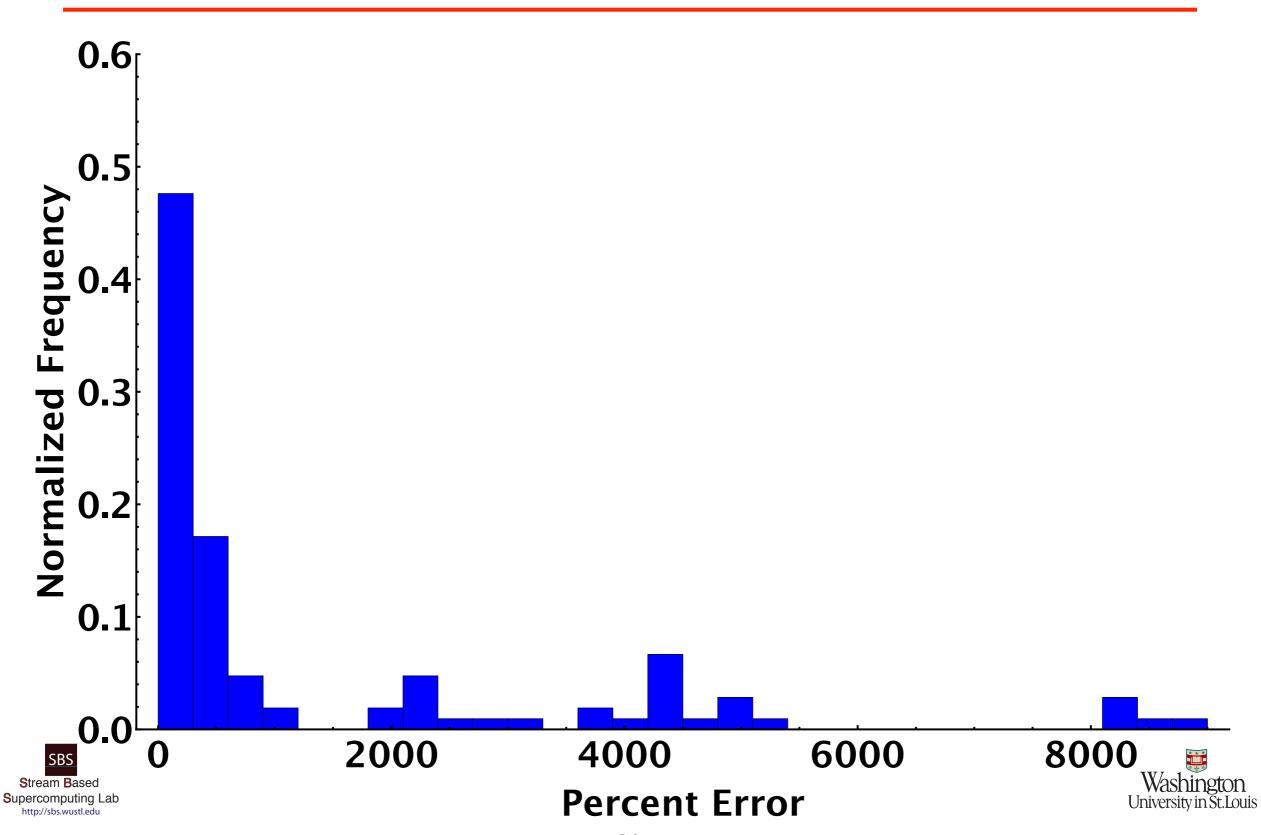

### **Queue Model Results**

Step I:

|   | Observed<br>Occupancy | Percent Error |

|---|-----------------------|---------------|

| M |                       | (M - 0 / 0)   |

Step 2:

Combine DES Encrypt, JPEG Encode and Synthetic Applications

Step 3:

Make a histogram

## **Queue Model Results**

### Conclusion

- Showed that a generalized maximum flow model can be used to solve for max flow of a queueing network.

- Demonstrated the flow model is reliable on real systems

- Simple M/M/I queueing model is insufficient to estimate buffering requirements

#### References

#### **Slides and Software**

http://sbs.wustl.edu